# UNIVERSITY OF MINES AND TECHNOLOGY, TARKWA

# FACULTY OF ENGINEERING DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING

# THESIS REPORT ENTITLED

MITIGATION OF HARMONICS IN POWER DISTRIBUTION SYSTEMS USING DISTRIBUTION STATIC COMPENSATOR

> BY CHRISTIAN DZAH

SUBMITTED IN FULFILLMENT OF THE REQUIREMENT FOR THE AWARD OF THE DEGREE OF MASTER OF PHILOSOPHY IN ELECTRICAL AND ELECTRONIC ENGINEERING

THESIS SUPERVISORS

DR FRANCIS B. EFFAH

MR ERWIN NORMANYO

TARKWA, GHANA MARCH 2019

#### **DECLARATION**

I declare that this thesis is my own work. It is being submitted for the degree of Master of Philosophy in Electrical and Electronic Engineering in the University of Mines and Technology (UMaT), Tarkwa. It has not been submitted for any degree or examination in any other University.

(Signature of Candidate)

..... day of June, 2019

#### ABSTRACT

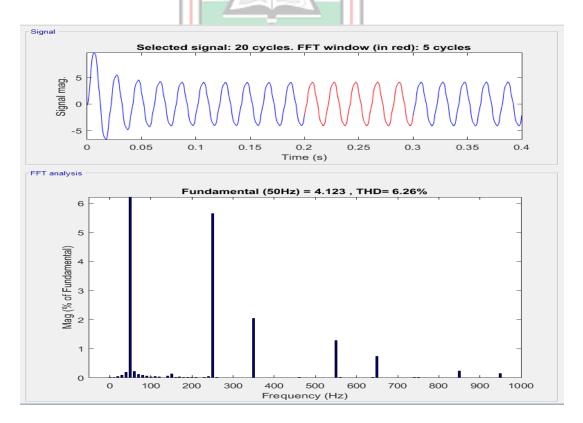

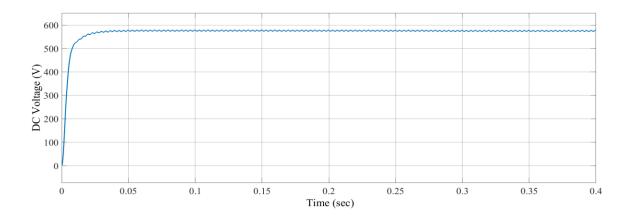

The quality of electric power is of major concern for both electric utilities and the end users of electric power in the wake of widespread use of nonlinear loads. Nonlinear loads normally draw non-sinusoidal (also called harmonics) currents and voltages at the point of connection with the utility grid and distribute them throughout the system causing protective relays and switchgear malfunctions, communication interference, incorrect meter readings, overheating of conductors, insulation degradation, and power transformer failures. In this research, focus was given to the harmonics generated by nonlinear loads using synchronous reference frame theory-based distribution static compensator. A distribution system having a stiff power source, linear and nonlinear loads, has been modelled in MATLAB/Simulink version 2017a software environment. For the control system design, proportional integral controllers were used for both voltage and current controls. Voltage source inverter with sinusoidal pulse width modulation was also employed for generating the alternating current. The investigation of harmonics by way of simulations, was carried out using the fast fourier transform from the MATLAB software to evaluate the total harmonic distortion generated by the nonlinear load with and without DSTATCOM connected. The simulation results indicated that at steady state voltage values of V<sub>dc</sub> of 489 V, 555 V and 575 V, the current THD stood at 5.71%, 6.89% and 6.26%, respectively after mitigation giving a minimum of 55.8% reduction of harmonics in the source current. The distribution static compensator stands to be recommended for current harmonics mitigation in low voltage distribution systems.

### **DEDICATION**

# To God Be the Glory

This thesis report is dedicated to the following:

My son

Ethan Senam Dzah

#### ACKNOWLEDGEMENTS

This thesis work has been completed not by my strength but through the grace of God, for He has been my support and protector throughout the programme.

At this point of my career, I know I am indebted to many individuals for their support, encouragement and guidance. I would therefore like to express my heartfelt gratitude to my gallant supervisors Dr Francis B. Effah and Mr Erwin Normanyo. Their guidance, technical discussions and constant encouragements accompanied with patience have actually helped me in the completion of this work. It is true that, their immense experience and understanding of the topic helped me in tackling some of the difficult challenges encountered in doing this research work. I thank them for all that they have done for me. I would like to acknowledge Dr Solomon Nunoo who is also the Head of Department, Electrical and Electronic Engineering, for his effort and countless enlightening conversations which led to the achievement of this goal. To all lecturers in the Electrical and Electronic Engineering Department, I say, thank you for the knowledge impacted in me.

Nothing in life is possible without the love and support from one's family. I would therefore like to express my sincere gratitude to my lovely wife Doris Mawufemor Adukpoh for her sacrifices, patience, support and unconditional love. I would like to express my undying love and gratitude to my mother Sesime Kumah Dzah (Mrs) and father Fritz K. Dzah for their lifetime support, encouragement and education. Their love and blessings made everything I have accomplished possible. I would also like to thank all my siblings for their prayers, constant support in diverse ways and encouragement. Last but not the least, I would like to express my gratitude to all my course mates for their support. May the almighty God continue to guard and guide each and every one of us for a better future.

# **TABLE OF CONTENTS**

| Cont | ent                                                  | Page         |

|------|------------------------------------------------------|--------------|

| DEC  | LARATION                                             | i            |

| ABS  | ГКАС                                                 | ii           |

| DED  | ICATION                                              | iii          |

| ACK  | NOWLEDGEMENTS                                        | iv           |

| TAB  | LE OF CONTENTS                                       | $\mathbf{V}$ |

| LIST | OF FIGURES                                           | ix           |

| LIST | OF TABLES                                            | xii          |

| LIST | OF ABBREVIATIONS                                     | xiii         |

| LIST | OF SYMBOLS                                           | XV           |

| INTE | ERNATIONAL SYSTE <mark>M OF UNITS (SI UNIT</mark> S) | xviii        |

| СНА  | PTER 1 GENERAL INTRODUCTION                          | 1            |

| 1.1  | Background to the Research                           | 1            |

| 1.2  | Problem Definition                                   | 2            |

| 1.3  | Purpose of the Research                              | 5            |

| 1.4  | Objectives of the Research                           | 5            |

| 1.5  | Expected Outcomes                                    | 5            |

| 1.6  | Research Questions and Hypothesis                    | 5            |

| 1.7  | Scope of the Research                                | 6            |

| 1.8  | Research Methods Used                                | 6            |

| 1.9  | Facilities Used for the Research                     | 6            |

| 1.10 | Significance of the Research                         | 6            |

| 1.11 | Limitations of the Research                          | 7            |

| 1.12 | Definition of Terms and Key Concepts                 | 7            |

| 1.13 | Organisation of the Thesis                           | 9            |

| СНА  | PTER 2 LITERATURE REVIEW                             | 10           |

| 2.1  | Introduction                                         | 10           |

| 2.2  | Harmonics in Power Distribution Systems              | 10           |

|      | 2.2.1  | Definition of Harmonics                                    | 11 |

|------|--------|------------------------------------------------------------|----|

|      | 2.2.2  | Harmonic Current                                           | 11 |

|      | 2.2.3  | Harmonic Voltage                                           | 12 |

|      | 2.2.4  | Harmonic Distortion                                        | 12 |

|      | 2.2.5  | Harmonic Phase Sequences                                   | 13 |

|      | 2.2.6  | Triplen Harmonics                                          | 13 |

|      | 2.2.7  | Harmonic Indices                                           | 13 |

| 2.3  | Harm   | onics Filtering Techniques                                 | 15 |

|      | 2.3.1  | Passive Filtering of Harmonics                             | 16 |

|      | 2.3.2  | Active Filtering of Harmonics                              | 17 |

|      | 2.3.3  | Hybrid Harmonic Filter                                     | 17 |

| 2.4  | Two-I  | Level Voltage Source Converter for Harmonic Mitigation     | 18 |

| 2.5  | Multil | evel Converter for Harmonic Mitigation                     | 19 |

|      | 2.5.1  | Diode Clamped Multilevel Inverter                          | 20 |

|      | 2.5.2  | Flying Capacitor Multilevel Inverter                       | 21 |

|      | 2.5.3  | Cascaded H-Bridge Multilevel Inverter                      | 23 |

|      | 2.5.4  | Hybrid H-Bridge Multilevel Inverter                        | 24 |

| 2.6  | Custo  | m Power Devices for Mitigation of Harmonics                | 24 |

|      | 2.6.1  | Distribution Static Compensator                            | 25 |

|      | 2.6.2  | Dynamic Voltage Restorer                                   | 27 |

|      | 2.6.3  | Unified Power Quality Controller                           | 27 |

| 2.7  | Propo  | rtional-Integral-Derivative Control                        | 28 |

| 2.8  | Revie  | w of Related Works on the Mitigation of Harmonics in Power | 31 |

|      | Distri | bution Systems                                             |    |

| 2.9  | Summ   | ary                                                        | 32 |

| CHAI | PTER 3 | 3 METHODOLOGY                                              | 34 |

| 3.1  | Introd | uction                                                     | 34 |

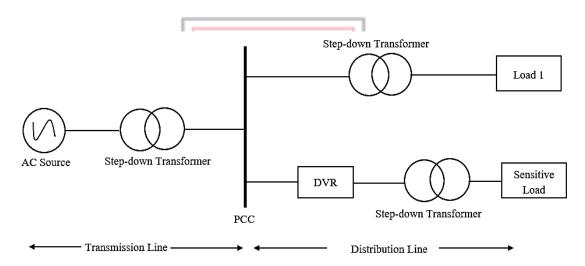

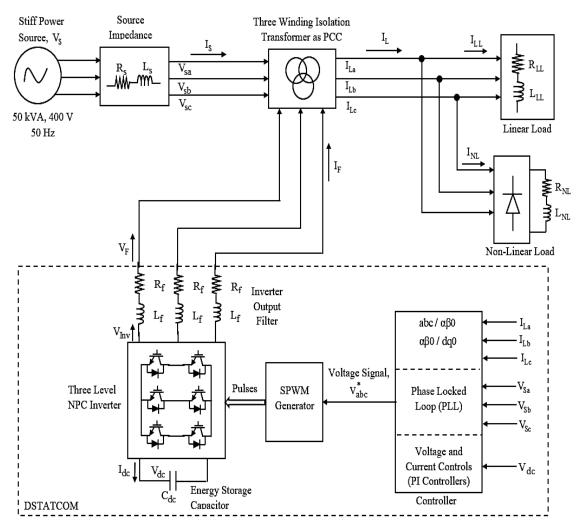

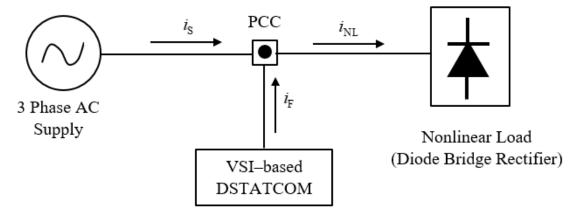

| 3.2  | Gener  | al Description of the Proposed System                      | 34 |

|      |        |                                                            |    |

| 3.3 | The AC Voltage Source                                           | 35 |

|-----|-----------------------------------------------------------------|----|

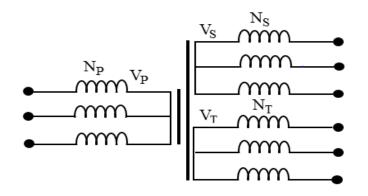

| 3.4 | The Three Winding Isolation Transformer                         | 37 |

| 3.5 | Resistive – Inductive Load and the Rectifier                    | 38 |

| 3.6 | Distribution Static Compensator                                 | 40 |

|     | 3.6.1 Operating Principle of DSTATCOM                           | 41 |

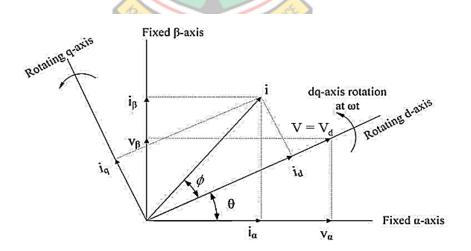

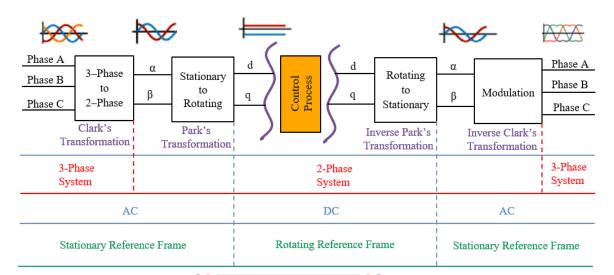

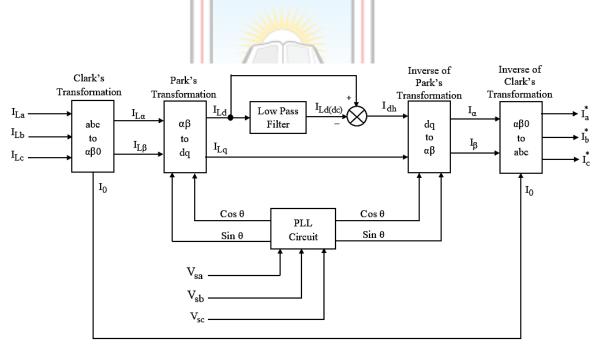

|     | 3.6.2 Synchronous Reference Frame Theory                        | 43 |

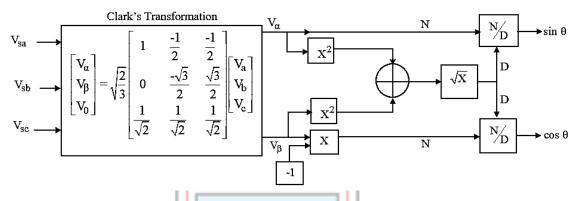

|     | 3.6.3 The Phase Locked Loop                                     | 47 |

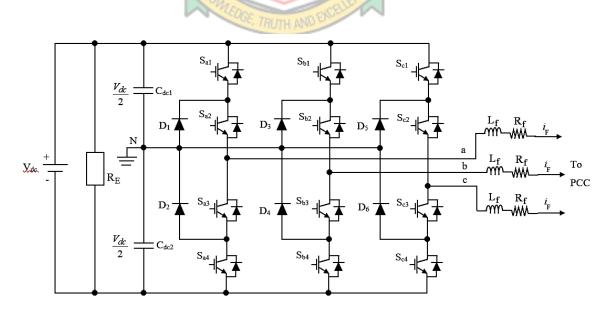

|     | 3.6.4 Three Level Neutral Point Clamped Voltage Source Inverter | 48 |

|     | 3.6.5 DC Capacitor and DC-Link Bus Voltage                      | 50 |

|     | 3.6.6 Inverter Output Filter                                    | 51 |

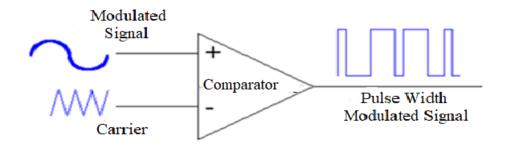

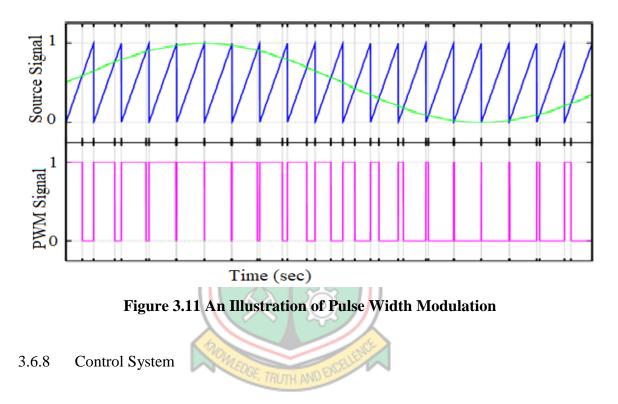

|     | 3.6.7 Sinusoidal Pulse Width Modulation Voltage Controller      | 52 |

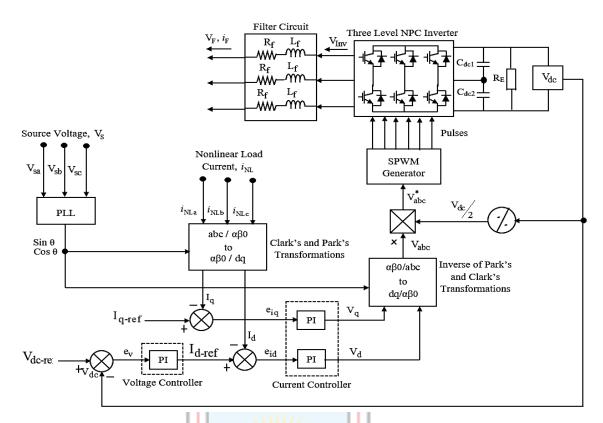

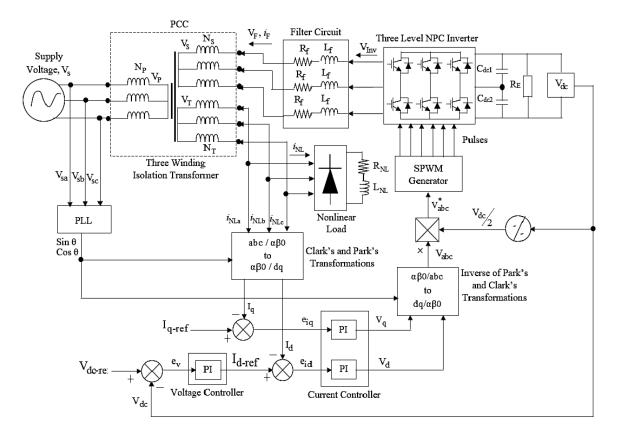

|     | 3.6.8 Control System                                            | 53 |

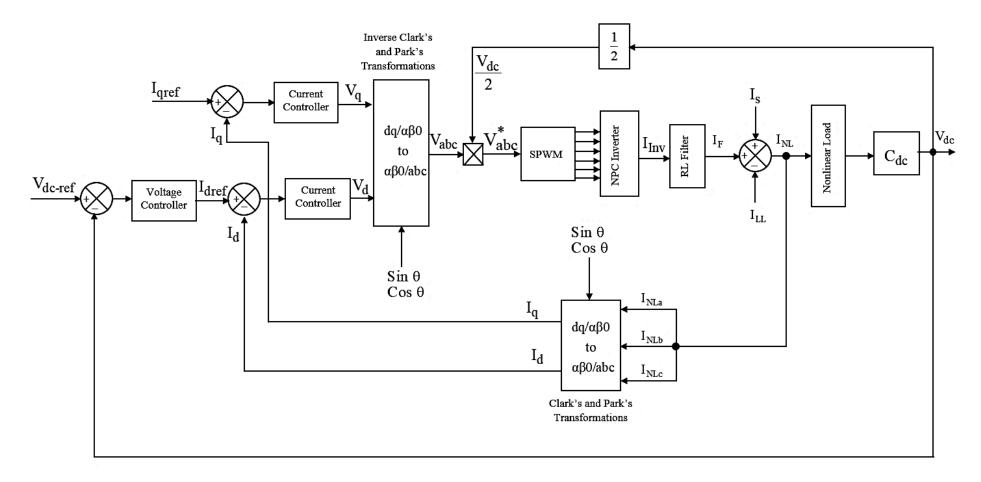

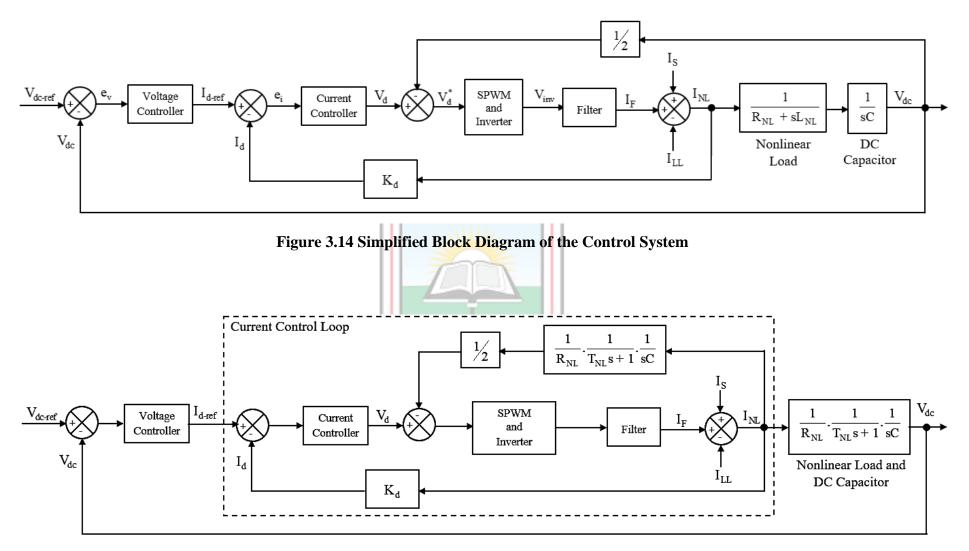

| 3.7 | Design of the Control System                                    | 54 |

|     | 3.7.1 Governing Equations of the Control System                 | 57 |

| 3.8 | Computer Simulations                                            | 63 |

| 3.9 | Summary                                                         | 65 |

| СНА | PTER 4 RESULTS AND DISCUSSIONS                                  | 66 |

|     | 20011500 - SEVERS                                               |    |

| 4.1 | Introduction                                                    | 66 |

| 4.2 | Simulation Test Results on the System                           | 66 |

| 4.3 | Simulation Results with and without DSTATCOM                    | 68 |

| 4.4 | Summary of Findings                                             | 76 |

| СНА | PTER 5 CONCLUSIONS AND RECOMMENDATIONS                          | 77 |

| 5.1 | Conclusions                                                     | 77 |

| 5.2 | Recommendations                                                 | 77 |

| 5.3 | Research Contributions                                          | 78 |

| 5.4 | Future Research Directions                                      | 78 |

| REFERENCES                                       | 79 |

|--------------------------------------------------|----|

| APPENDICES                                       | 87 |

| APPENDIX A HARMONICS STANDARDS                   | 87 |

| APPENDIX B C-SOURCE CODES FOR THE CONTROL SYSTEM | 88 |

#### LIST OF FIGURES

#### Figure Title Page 1.1 Harmonic Waveforms Superimposed on the Fundamental Frequency Signal 4 1.2 Distorted Wave Composed by the Superposition of a 50 Hz Fundamental 4 and Smaller 3<sup>rd</sup> and 5<sup>th</sup> Harmonics 2.1 Voltage Harmonic Waveforms as a Result of Nonlinear Loads 11 2.2 Typical Current Waveform due to Nonlinear Load 12 2.3 Schematic Diagram of the Connection of Passive Filter 16 2.4 Schematic Diagram of Active Shunt Filter with Nonlinear Load 17 2.5 Schematic Diagram of Hybrid Power Filter as a Combination of Active 18 Shunt and Passive Shunt Filters 2.6 Three Phase Two Level Voltage Source Converter 19 2.7 Types of Multilevel Inverter Topologies 20 2.8 21 Schematic Diagram of Three Level Diode Clamped Inverter 2.9 Schematic Diagram of Three Level Flying Capacitor Inverter 22 2.10 Schematic Diagram of Cascaded H-Bridge Multilevel Inverter 23 2.11 Schematic Diagram of Hybrid H-Bridge Multilevel Inverter 24 2.12 Current Source Converter-based DSTATCOM 26 2.13 Voltage Source Converter-based DSTATCOM 26 2.14 Location of a Dynamic Voltage Restorer 27 2.15 Block Diagram of Unity Feedback Control System 28 3.1 Block Diagram of the Designed System 35 3.2 Circuit Diagram of a Three Winding Transformer 38 3.3 Block Diagram of the Structure of DSTATCOM 41 3.4 Simplified Configuration of VSI-based DSTATCOM 41 3.5 Phasor Diagram of D-Q Transformation 43 3.6 44 **Control Stages and Respective Reference Frame** 3.7 Block Diagram of Synchronous Reference Frame based Reference Current 44 Extraction 3.8 48 Block Diagram of the Phase Locked Loop 3.9 The Three Level Neutral Point Clamped Voltage Source Inverter 49

| 3.10 | Simplified Model of a Comparator                                   | 53 |

|------|--------------------------------------------------------------------|----|

| 3.11 | An Illustration of Pulse Width Modulation                          | 53 |

| 3.12 | Block Diagram of the Control Structure of DSTATCOM                 | 54 |

| 3.13 | General Block Diagram of the Closed Loop Control System            | 55 |

| 3.14 | Simplified Block Diagram of the Control System                     | 56 |

| 3.15 | Block Diagram Depicting the Voltage and Current Control Loop       | 56 |

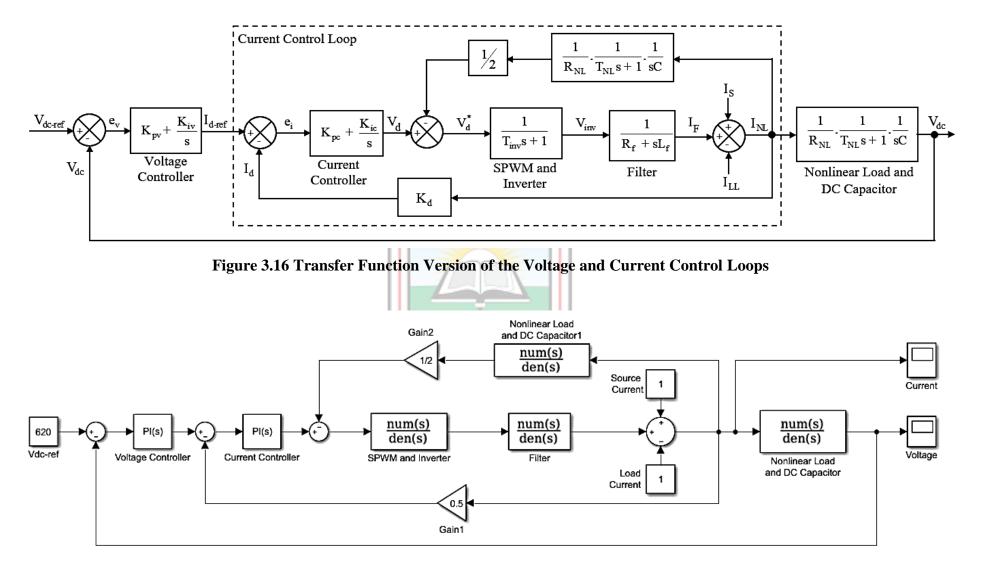

| 3.16 | Transfer Function Version of the Voltage and Current Control Loops | 61 |

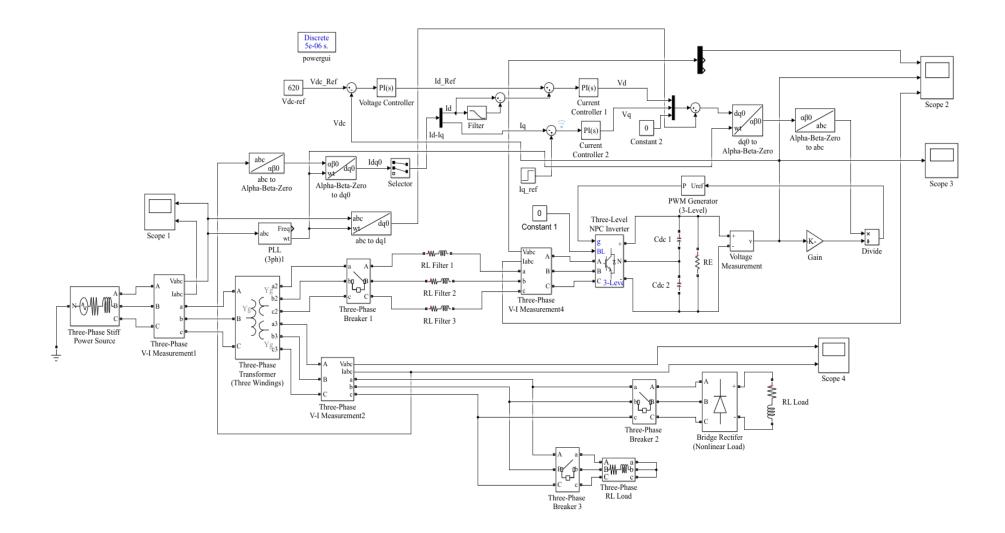

| 3.17 | Simulink Implementation for the Control System                     | 61 |

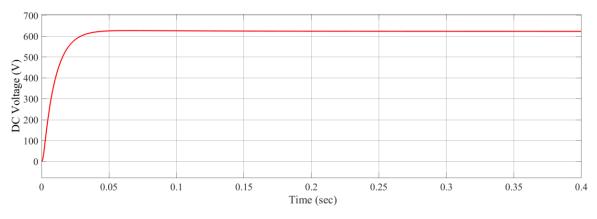

| 3.18 | Response of the Control System for the First Case                  | 62 |

| 3.19 | Response of the Control System for the Second Case                 | 62 |

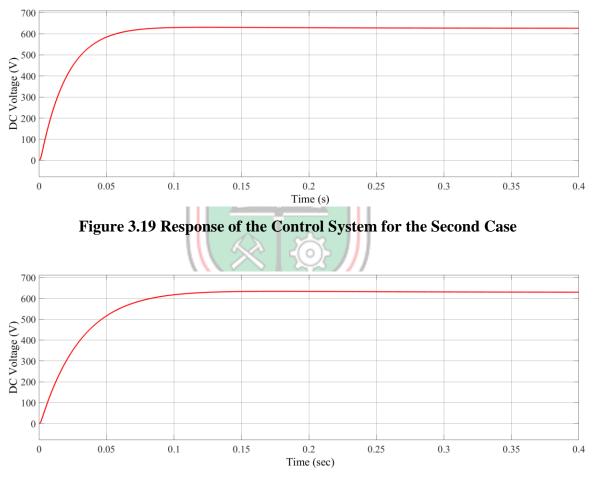

| 3.20 | Response of the Control System for the Third Case                  | 62 |

| 3.21 | The Complete Circuit Implementation of Proposed System in          | 64 |

|      | MATLAB/Simulink Software                                           |    |

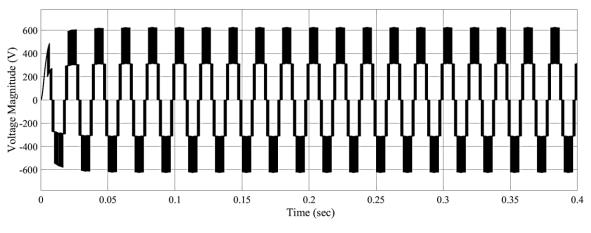

| 4.1  | Line – to – Line Stepped Output Voltage of 3-Level NPC Inverter    | 67 |

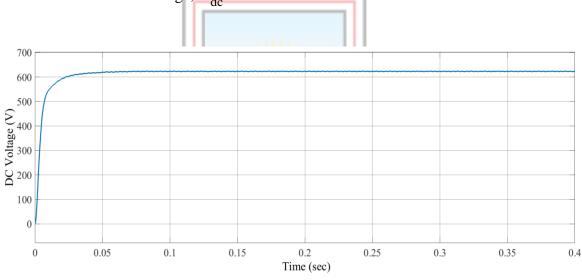

| 4.2  | Response of the Control System                                     | 67 |

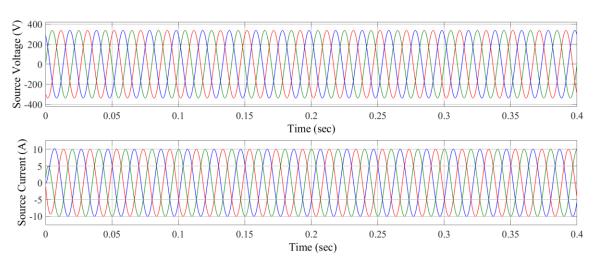

| 4.3  | Source Voltage and Current Waveforms with Linear Load Connected    | 68 |

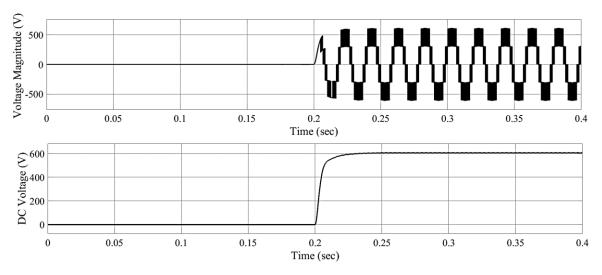

| 4.4  | Line – to – Line Output Voltage of VSI and Response of the System  | 68 |

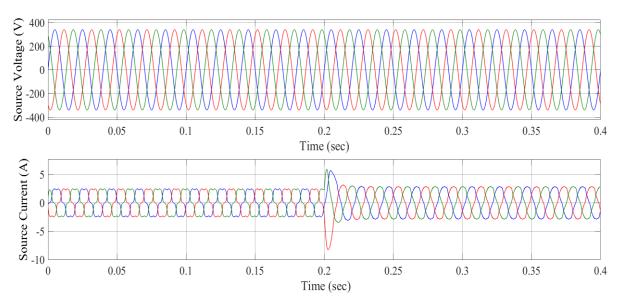

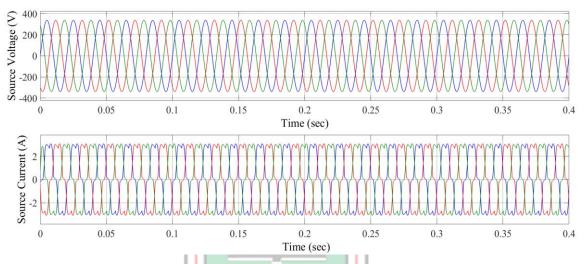

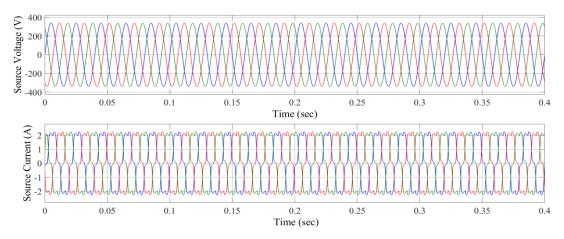

| 4.5  | Source Voltage and Current Waveforms for Nonlinear Load with       | 69 |

|      | DSATACOM Connected at 0.2 secs                                     |    |

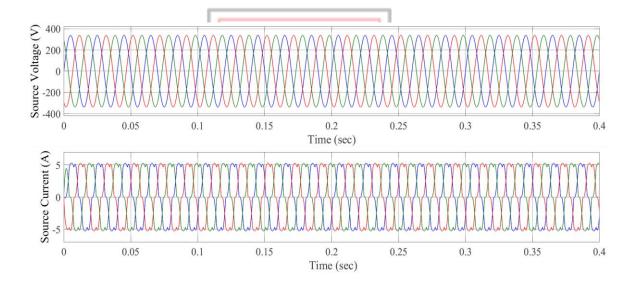

| 4.6  | Source Voltage and Current Waveforms with Nonlinear Load 1 without | 70 |

|      | DSTATCOM                                                           |    |

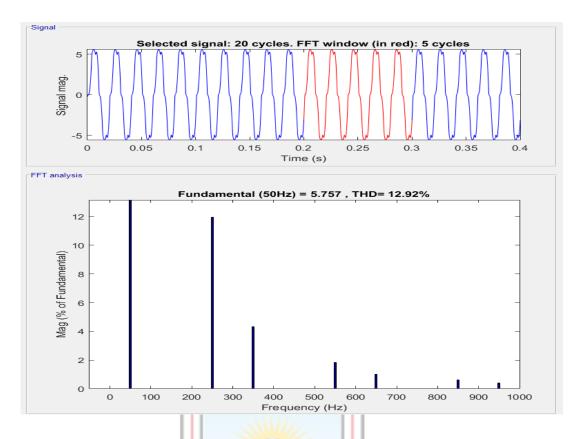

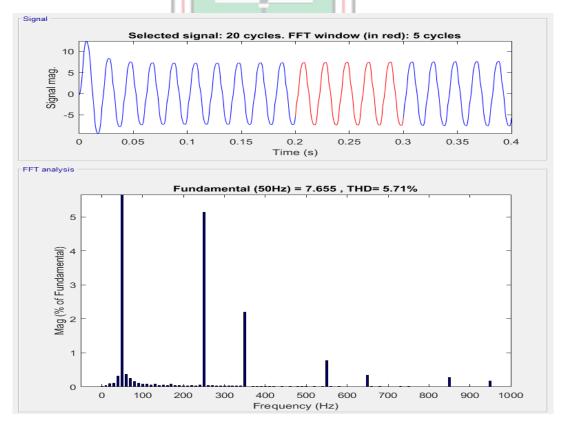

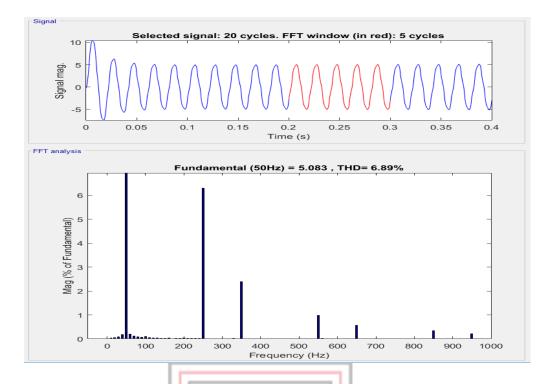

| 4.7  | Result of FFT Analysis of Source Current without DSTATCOM showing  | 71 |

|      | waveform and Spectrum                                              |    |

| 4.8  | Result of FFT Analysis of Source Current with DSTATCOM showing     | 71 |

|      | waveform and Spectrum                                              |    |

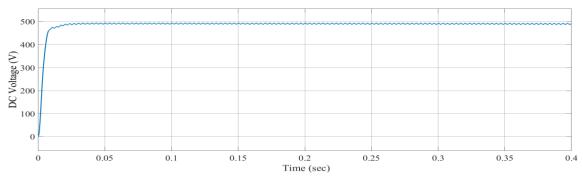

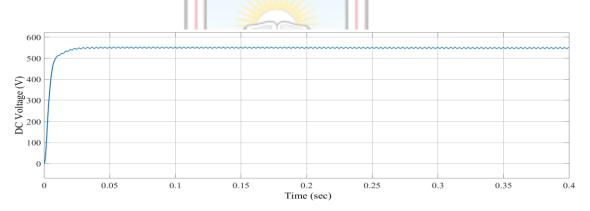

| 4.9  | Response of the Control System when "Load 1" is Connected          | 72 |

| 4.10 | Source Voltage and Current Waveforms with Nonlinear Load 2 without | 72 |

|      | STATCOM                                                            |    |

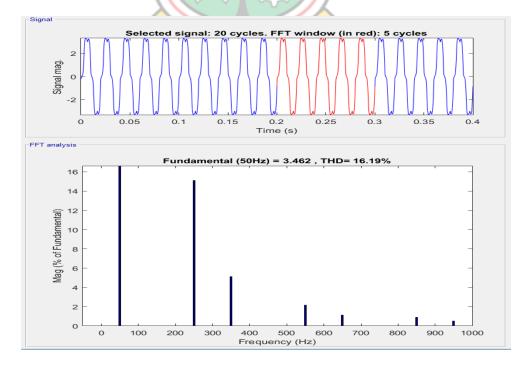

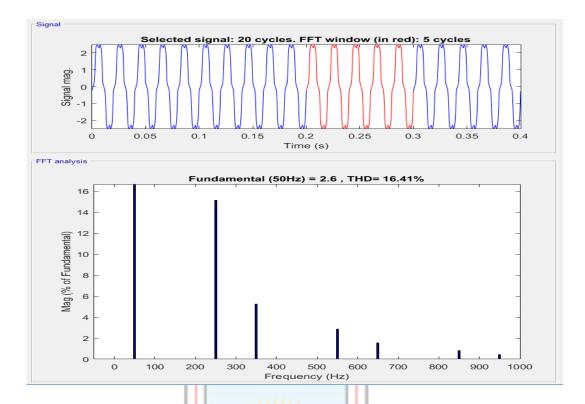

| 4.11 | Result of FFT Analysis of Source Current without DSTATCOM showing  | 72 |

|      | waveform and Spectrum                                              |    |

| 4.12 | Result of FFT Analysis of Source Current without DSTATCOM showing  | 73 |

|      | waveform and Spectrum                                              |    |

| 4.13 | Response of the Control System when "Load 2" is Connected          | 73 |

|      |                                                                    |    |

| 4.14 | Source Voltage and Current Waveforms with Nonlinear Load 3 without | 73 |

|------|--------------------------------------------------------------------|----|

|      | DSTATCOM                                                           |    |

| 4.15 | Result of FFT Analysis of Source Current without DSTATCOM showing  | 74 |

|      | waveform and Spectrum                                              |    |

| 4.16 | Result of FFT Analysis of Source Current with DSTATCOM showing     | 74 |

|      | waveform and Spectrum                                              |    |

| 4.17 | Response of the Control System when "Load 3" is Connected          | 75 |

## LIST OF TABLES

# TableTitlePage2.1Effect of PID Controller Gain Parameters on a Control System293.1Switching States of the Three-Level Neutral Point Clamped VSI504.1System Parameters used in the Simulation66

| 4.2 | Total Harmonic Distortion of the Source Current, $i_{s}$ before and after | 75 |

|-----|---------------------------------------------------------------------------|----|

|     | Mitigation                                                                |    |

# LIST OF ABBREVIATIONS

#### Abbreviation

# Meaning

| AC       | Alternating Current                               |

|----------|---------------------------------------------------|

| BFOA     | Bacteria Foraging Optimisation Algorithm          |

| ССМ      | Current Control Mode                              |

| CPD      | Custom Power Device                               |

| CSI      | Current Source Inverter                           |

| DC       | Direct Current                                    |

| DCLV     | DC Link Voltage                                   |

| DSTATCOM | Distribution Static Compensator                   |

| DVR      | Dynamic Voltage Restorer                          |

| ECG      | Electricity Company of Ghana                      |

| FACTS    | Flexible Alternating Current Transmission Systems |

| FFT      | Fast Fourier Transform                            |

| GSA      | Gravitational Search Algorithm                    |

| HAPF     | Hybrid Active Power Filter                        |

| IEEE     | Institute of Electrical and Electronic Engineers  |

| IGBT     | Insulated Gate Bipolar Transistor                 |

| IRP      | Instantaneous Reactive Power                      |

| LCL      | Inductor Capacitor Inductor                       |

| LPF      | Low Pass Filter                                   |

| LSPWM    | Level Shifted Pulse Width Modulation              |

| MCPWM    | Multi-Carrier Pulse Width Modulation              |

| MLI      | Multilevel Inverter                               |

| NPC      | Neutral Point Clamped                             |

| PCC      | Point of Common Coupling                          |

| PI       | Proportional Integral                             |

| PID      | Proportional Integral Derivative                  |

| PLL      | Phase Locked Loop                                 |

| PQ       | Power Quality                                     |

| PR       | Proportional Resonance                            |

|          |                                                   |

| PSO              | Particle Swarm Optimisation          |

|------------------|--------------------------------------|

| PSPWM            | Phase Shifted Pulse Width Modulation |

| PWM              | Pulse Width Modulation               |

| SAPF             | Shunt Active Power Filter            |

| SCR              | Silicon Control Rectifier            |

| SPWM             | Sinusoidal Pulse with Modulation     |

| SRF              | Synchronous Reference Frame          |

| SVC              | Static Var Compensator               |

| TDD              | Total Demand Distortion              |

| THC              | Total Harmonic Current               |

| THD              | Total Harmonic Distortion            |

| THD <sub>I</sub> | Total Harmonic Current Distortion    |

| THD <sub>V</sub> | Total Harmonic Voltage Distortion    |

| UPQC             | Unified Power Quality Compensator    |

| VSC              | Voltage Source Converter             |

| VSI              | Voltage Source Inverter              |

|                  | ROMADRE TRUTH AND EXCLUSION          |

# LIST OF SYMBOLS

| Amplitude of the current harmonic                      | I <sub>n</sub>            |

|--------------------------------------------------------|---------------------------|

| Amplitude of the fundamental current                   | $I_1$                     |

| Actual output signal                                   | Y(s)                      |

| Angular frequency of the waveform                      | ω                         |

| Cycle that start working the controller                | n                         |

| Current drawn by the rectifier                         | Ir                        |

| Current ripple factor                                  | I <sub>crp</sub>          |

| Controller output signal                               | U(s)                      |

| Desired input signal                                   | R(s)                      |

| DC voltage                                             | V <sub>dc</sub>           |

| Derivative gain                                        | K <sub>d</sub>            |

| DC current                                             | I <sub>dc</sub>           |

| DC link charging current                               | i <sub>dc</sub>           |

| DC capacitor                                           | C <sub>dc</sub>           |

| Damping coefficient                                    | ξ                         |

| Error                                                  | e                         |

| Equalizing resistance                                  | $R_{E}$                   |

| Fundamental frequency                                  | $\mathbf{f}_{\mathbf{o}}$ |

| Full Load fundamental current                          | $I_L$                     |

| Filter current                                         | $I_{F}$                   |

| Harmonic frequency                                     | $\mathbf{f}_{\mathbf{h}}$ |

| Harmonic component in the load current of the d – axis | I <sub>dh</sub>           |

| Instantaneous current supply                           | is                        |

| Instantaneous load current                             | $i_L$                     |

| Instantaneous converter current                        | i <sub>C</sub>            |

| Integral gain                                          | K <sub>i</sub>            |

| Integral gain of voltage                               | K <sub>iv</sub>           |

| Instantaneous direct current         | i <sub>d</sub>      |

|--------------------------------------|---------------------|

| Instantaneous quadrature current     | iq                  |

| Injected current                     | I <sub>inj</sub>    |

| Integer number                       | h                   |

| Interface inductor                   | $L_{f}$             |

| Interface resistor                   | R <sub>f</sub>      |

| Line – to – line grid voltage        | V <sub>LL</sub>     |

| Load current in the $\alpha$ - axis  | $I_{L\alpha}$       |

| Load current in the $\beta$ - axis   | $I_{L\beta}$        |

| Load current in the d – axis         | I <sub>Ld</sub>     |

| Load current in the q – axis         | I <sub>Lq</sub>     |

| Modulation index                     | m                   |

| Number of output voltage levels      | NL                  |

| Number of switches                   | NS                  |

| Number of voltage sources            | S                   |

| Natural frequency                    | ω <sub>n</sub>      |

| Overloading factor                   | а                   |

| Phase difference                     | $\phi$              |

| Proportional gain                    | K <sub>p</sub>      |

| Proportional gain of voltage         | K <sub>pv</sub>     |

| Power rating of the system           | S <sub>n</sub>      |

| Peak value of the grid phase voltage | V <sub>m</sub>      |

| Quadrature load current              | I <sub>Lq</sub>     |

| Quadrature reference current         | I <sub>q_ref</sub>  |

| Quadrature voltage                   | Vq                  |

| Reference dc current                 | I <sub>dc_ref</sub> |

| Reference dc voltage                 | V <sub>dc_ref</sub> |

| Reference current                                | I <sub>ref</sub>      |

|--------------------------------------------------|-----------------------|

| rms AC voltage                                   | V <sub>ar</sub> (rms) |

| Source current                                   | IS                    |

| Source voltage                                   | V <sub>S</sub>        |

| Source impedance                                 | $Z_S$                 |

| Source resistance                                | R <sub>S</sub>        |

| Source reactance                                 | X <sub>S</sub>        |

| Source inductance                                | $L_S$                 |

| Switching frequency                              | f <sub>s</sub>        |

| Total AC current drawn by rectifier and R-L load |                       |

| Transformation angle                             | θ                     |

| Time period of the system                        | Т                     |

| Voltage drop                                     | V <sub>dp</sub>       |

| Voltage available to the load                    | Vo                    |

| Voltage at the PCC                               | V <sub>tpcc</sub>     |

| Voltage in the d – axis                          | V <sub>d</sub>        |

| Voltage in the q – axis                          | Vq                    |

# **INTERNATIONAL SYSTEM OF UNITS (SI UNITS)**

| Quantity             | Unit    | Symbol |

|----------------------|---------|--------|

|                      |         |        |

| Time                 | seconds | S      |

| Frequency            | hertz   | Hz     |

| Electric current     | ampere  | А      |

| Electric potential   | volt    | V      |

| Electric resistance  | ohm     | Ω      |

| Electric capacitance | farad   | F      |

| Inductance           | henry   | Н      |

#### **CHAPTER 1**

#### **GENERAL INTRODUCTION**

#### **1.1 Background to the Research**

A pure sinusoidal waveform with zero harmonic distortion is said to be a hypothetical quantity and not practical. The reason being that, even the voltage waveform at the point of generation, contains small amounts of distortion due to non-uniformity in the excitation magnetic field and discrete spatial distribution of coils around the generator stator slots. The distortion at the point of generation is usually very low, typically less than 1.0% (Basim, 2017). The generated voltage is transmitted many hundreds of kilometers, transformed to several levels, and finally distributed to the power consumer. The main objective of the electric utility is to deliver sinusoidal voltage at fairly constant magnitude throughout their system (Jaisiva *et al.*, 2016). The user equipment generates currents that are rich in harmonic frequency components, especially in large commercial or industrial installations. As harmonic currents travel to the power source, the current distortion results into additional voltage distortion due to impedance voltages associated with the various power distribution equipment, such as distribution lines, transformers, cables, and buses. The harmonic distortion is the major source of sine waveform distortion (Priya *et al.*, 2016).

Harmonics are the major source of sinusoidal waveform distortion. Harmonics have become more common in power systems now. Harmonic distortion is caused by nonlinear loads in power systems (Ali *et al.*, 2016). Nonlinear loads are referred to as loads in which the current is not proportional to the applied voltage (Jaisiva *et al.*, 2016). In short, harmonics are integral multiples of the fundamental frequency of the sinusoidal wave that is, harmonics are multiples of the 50 Hz or 60 Hz fundamental voltage and current.

According to Fourier theory, a periodic waveform can be expressed as a sum of pure sine waves of different amplitudes where the frequency of each sinusoid is an integer multiple of the fundamental frequency of the periodic waveform (Jaisiva *et al.*, 2016). A frequency that is an integer multiple of the fundamental frequency is called harmonic frequency, i.e.  $f_h = hf_o$  where  $f_o$  and h are the fundamental frequency and an integer number, respectively.

Harmonics in power systems can lead to system failure if not mitigated. The following are some of the ways by which harmonics may affect the power distribution system (Eyad, 2016):

- i. Overheating of conductors;

- ii. Failure of capacitor due to heat rise;

- iii. False operations and tripping of fuses and circuit breakers;

- iv. Excessive overheating in the transformer;

- v. Interference and operation instability of generators;

- vi. Utility meters may record measurements incorrectly, resulting in higher billings to consumers;

- vii. Harmonics can cause failure of the commutation circuits, found in DC drives and AC drives with Silicon Controlled Rectifiers (SCRs); and

- viii. Computers/telephones may experience interference or failures.

Distribution Static Compensator (DSTATCOM) is the most effective device that can be used in mitigating harmonics in distribution systems (Priya *et al.*, 2016). The primary function of the DSTATCOM is to control the reactive power and also to regulate voltage. It was found that voltage fluctuations were reduced from 2.5% to 0.2% by the use of DSTATCOM (Rani and Jyothi, 2011). This reduces voltage flicker substantially (Bhim *et al.*, 2015; Padiyar, 2007). Therefore, in this research, DSTATCOM will be used as a device for mitigating harmonics in order to unravel the effect of harmonics in power distribution systems. In Ghana, the frequency of power generated is 50 Hz therefore this frequency will be considered in this thesis report.

#### **1.2 Problem Definition**

In reality, the supplied voltage to customers' equipment and the resulting load currents are supposed to be perfect sine waves. But in practice, however, since conditions sometimes are never ideal, these waveforms are often in one way or the other distorted. This deviation from the perfect sinusoidal waveform is usually expressed in terms of harmonic distortion of the voltage and current waveforms. Harmonic distortion in power systems has become a major concern due to the fact that some devices or equipment used by consumers generate currents that are rich in harmonic frequency components such as harmonic current, in large commercial or industrial installations. The effects of harmonics are classified into four main categories such as (Snehal and Dnyaneshwar, 2016):

- i. Power system itself;

- ii. Consumer load;

- iii. Communication circuits; and

- iv. Revenue billing.

In power systems, harmonic currents are the main cause of equipment overheating. The impact is worse when network resonances amplify harmonic currents. Harmonics may also interfere with relaying and metering to some degree. Harmonics can lead to thyristor firing errors in converters and Static Var Compensator (SVC) installations, metering inaccuracies, and false tripping of protective devices. The performance of consumer equipment, such as motor drives and computer power supplies, can be adversely affected by harmonics. In addition, harmonic currents flowing in power lines can induce noise on nearby communication lines.

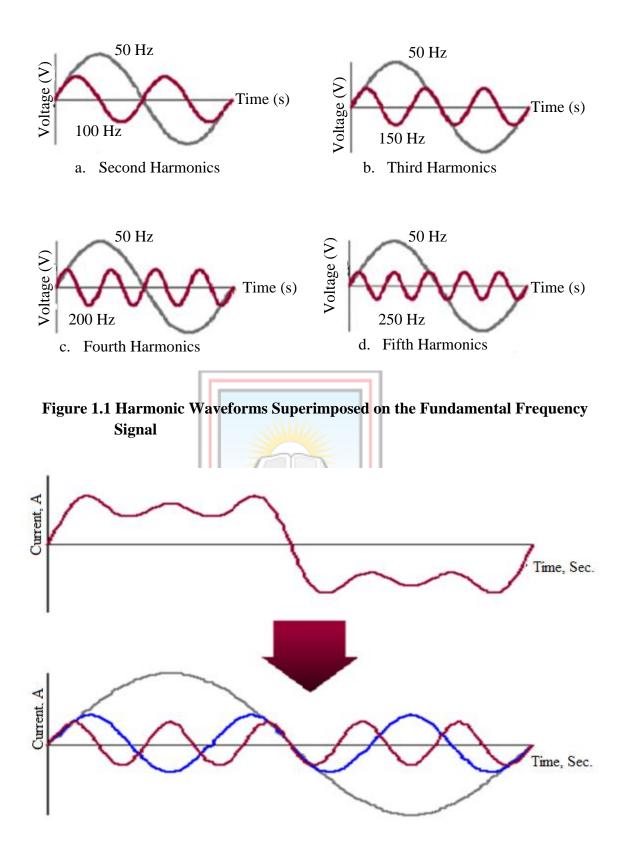

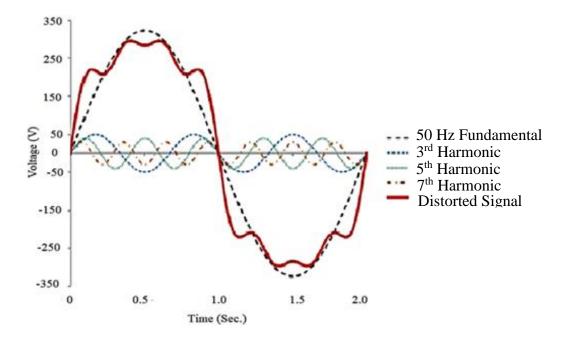

Harmonic voltage distortion may cause equipment insulation stress, particularly in capacitors. When harmonics cause the voltage impressed on the capacitor bank to be distorted, the peak voltage may be high enough to cause a partial discharge, or corona, within the capacitor dielectric. This may eventually result in a short circuit at the edges of the foil and failure of the capacitor bank. Figure 1.1 (Anon., 2014) illustrates harmonic waveforms superimposed on the fundamental frequency signal. Also, Figure 1.2 (Anon., 2014) illustrates distorted wave composed by the superposition of a 50 Hz fundamental and 3<sup>rd</sup> and 5<sup>th</sup> harmonics.

Figure 1.2 Distorted Wave Composed by the Superposition of a 50 Hz Fundamental and 3<sup>rd</sup> and 5<sup>th</sup> Harmonics

#### **1.3** Purpose of the Research

The purpose of this research is to utilise a Custom Power Device (CPD) in solving a currentbased power quality problem in electric power distribution system.

#### **1.4 Objectives of the Research**

The main objective of this research is to mitigate harmonics in power distribution systems using DSTATCOM. This can be achieved through the following specific objectives:

- i. To develop control algorithm for the DSTATCOM implementation; and

- ii. To validate the use of DSTATCOM in mitigating the inherent high harmonic content in power distribution system through modelling and computer simulations using MATLAB/Simulink power system environment.

#### 1.5 Expected Outcomes

At the end of this research, the expectations are that:

- i. There will be a DSTATCOM-based device which when connected to the distribution system will reduce the harmonic content;

- ii. The effect of harmonic distortion in distribution systems can be reduced; and

- iii. The problem of power quality which is due to harmonics can be reduced.

#### **1.6** Research Questions and Hypothesis

This research is being guided by the following questions:

- i. What are harmonics distortion in electric power distribution systems?

- Can high harmonic content in power distribution systems be reduced using DSTATCOM?

The research hypothesis is stated as follows: The inherent high harmonic content in electric power distribution systems can be mitigated to acceptable levels using DSTATCOM.

#### **1.7** Scope of the Research

This research work is limited to 400 volts electric power distribution systems, which is used to send power to consumer's premises. The main issue is to solve the current related power quality problem of harmonics associated with power distribution systems in Ghana. With this, the focus of this work is to mitigate current harmonics which normally return to the source of supply before resulting into voltage harmonics.

#### **1.8 Research Methods Used**

The research methods employed include the following:

- i. Review of related literature that are in the domain of the research topic from books, journals and other recognized publications;

- ii. Modelling of the power and control circuits of the DSTATCOM; and

- iii. Computer simulations using MATLAB/Simulink power system environment.

#### **1.9 Facilities Used for the Research**

Facilities used for this research work include:

- i. Internet, Library, Laboratory and Computer Facilities at UMaT and Ho Technical University; and

- ii. Laptop Computer with MATLAB/Simulink Software.

#### **1.10** Significance of the Research

Harmonic distortion is still the most significant power quality problem in power systems. High harmonic content in power systems can cause damage to transformers, cables, capacitor banks, failure of protective devices and can interfere with the energy meters leading to high bills to customers. Therefore, this research will help find solutions to various effects associated with harmonic distortion. More also, it will serve utility companies such as Power Distribution Services (PDS) Ghana, from spending more money on damaged equipment due to harmonics and also the consumers' from receiving high electricity bills.

#### 1.11 Limitations of the Research

The limitation of this research is that, the conclusions drawn from this research are only based on the simulation results, without practical implementation of the system.

#### **1.12** Definition of Terms and Key Concepts

*Harmonic component*: It is the component of order greater than one of the Fourier series of a periodic quantity.

*Harmonic content*: It is the quantity obtained by subtracting the fundamental component from an alternating quantity.

Harmonic distortion: It is the periodic distortion of the sine wave.

*Harmonic filter*: It is a device for filtering one or more harmonics from the power system. Active and passive filters are the most commonly used harmonic filters.

*Harmonic number*: It is the integral number given by the ratio of the frequency of a harmonic to the fundamental frequency.

*Harmonic resonance*: It is the condition in which the power system is resonating near one of the major harmonics being produced by nonlinear elements in the system, thus exacerbating the harmonic distortion.

*Impulsive transient*: It is a sudden, non-power frequency change in the steady-state condition of voltage or current that is unidirectional in polarity (primarily either positive or negative).

*Instantaneous*: It is used to quantify the duration of a short-duration variation as a modifier. This term refers to a time range from one-half cycle to 30 cycles of the power frequency.

*Interharmonic component*: It is a frequency component of a periodic quantity that is not an integer multiple of the frequency at which the supply system is designed to operate (e.g., 50 or 60 Hz).

*Inverter*: It is a power electronic device that converts direct current to alternating current of either power frequency or a frequency required by an industrial process.

*Linear load*: It is an electrical load device that, in steady-state operation, presents essentially constant load impedance to the power source throughout the cycle of applied voltage.

*Nonlinear load*: It is an electrical load that draws current discontinuously or presents impedance that varies throughout the cycle of the input ac voltage waveform.

*Notch*: It is a switching (or other) disturbance of the normal power voltage waveform, lasting less than a half-cycle, which is initially of opposite polarity than the waveform and is thus subtracted from the normal waveform in terms of the peak value of the disturbance voltage.

*Total demand distortion*: It is the ratio of the root mean square of the harmonic current to the rms value of the rated or maximum demand fundamental current, expressed as a percentage.

*Total harmonic distortion*: It is the ratio of the root mean square of the harmonic content to the rms value of the fundamental quantity, expressed as a percentage of the fundamental.

*Pulse-width modulation*: It is a common technique used in inverters to create an ac waveform by controlling the electronic switch to produce varying width pulses.

*Overvoltage*: It is used to describe a specific type of long-duration variation, and refers to a voltage having a value of at least 10 percent above the nominal voltage for a period of time greater than one minute.

*Passive filter*: It is the combination of inductors, capacitors, and/or resistors designed to eliminate one or more harmonics. The most common variety is simply an inductor in series with a shunt capacitor, which short-circuits the major distorting harmonic component from the system.

*Active filter*: This type of filter uses power electronic switching to generate harmonic current that cancel the harmonic current from a nonlinear load.

*Hybrid filter*: It is based on the combination of active and passive filters. Such a combination with the passive filter makes it possible to significantly reduce the rating of the active filter.

*Phase shift*: It is the displacement in time of one voltage waveform relative to other voltage waveform(s).

*Point of common coupling*: Point on a public power supply system, electrically nearest to a particular load, at which other loads are, or could be, connected. It is a point located upstream of the considered installation.

#### 1.13 Organisation of the Thesis

This thesis work consists of five chapters arranged as follows:

Chapter 1 covers background to the research, problem definition, purpose of the research, objectives of the research, expected outcomes, research questions and hypothesis, scope of the research, research methods used, facilities used for the research, significance of the research, limitations of the research, definition of terms and key concepts.

Chapter 2 reviews the literature on harmonic mitigation methods for power distribution systems. It also discusses the use of Custom Power Devices (CPD) with the control algorithms and filters.

Chapter 3 covers the research methodology and focuses on general description of the system, power distribution system, DSTATCOM for harmonic mitigation, design of the control system and computer simulations.

Chapter 4 gives the results, discussions and the summary of findings.

Chapter 5 covers the conclusions, recommendations, research contributions and future research directions.

#### **CHAPTER 2**

#### LITERATURE REVIEW

#### 2.1 Introduction

This chapter of the thesis actually discusses and reviews contributions of other researchers in the domain of the research topic. This is done in order to acquire more knowledge about the research topic chosen, the concepts involved and any other related information in order to improve upon the already existing works. The review is centered on harmonics in power distribution systems; harmonic mitigation techniques; power electronic converters for harmonics mitigation; custom power devices and control system for the mitigation of harmonics.

#### 2.2 Harmonics in Power Distribution Systems

Generally, power distribution systems in Ghana are designed to operate at a fundamental frequency of 50 Hz. However, there are certain types of loads that produce currents and voltages with frequencies that are integer multiples of the 50 Hz. These higher frequencies are a form of electrical pollution known as power system harmonics. Harmonics are generated by any load, which draws current not proportional to the voltage applied. Most loads are to some extent nonlinear, but some generate more and higher level of harmonics than others.

A "linear" load connected to an electric power system is defined as a load which draws current from the supply which is proportional to the applied voltage. A load is considered to be "nonlinear" if its impedance changes with the applied voltage. Due to the change in impedance, the current drawn by the nonlinear load is also nonlinear i.e. non-sinusoidal in nature, even when it is connected to a sinusoidal voltage source.

The main difference between linear and nonlinear loads is that, linear loads absorb electrical power linearly hence, their current waveforms remain sinusoidal in nature whereas non-linear loads absorb electrical power in a nonlinear manner hence the current drawn by them becomes non-sinusoidal in nature and therefore, distorted (Contractor *et al.*, 2015).

#### 2.2.1 Definition of Harmonics

Harmonic component in a power distribution system can be defined as the sinusoidal component of a periodic waveform that has a frequency equal to an integer multiple of the fundamental frequency of the system  $f_h = h \times$  fundamental frequency, where h is the integer to be multiplied. Periodic waveforms occurring at frequencies of 2f, 4f, 6f, 8f etc. are called even harmonics; whiles those with frequencies of 3f, 5f, 7f, 9f etc. are called odd harmonics. Although, harmonics are classified as even and odd harmonics, even harmonics get cancelled due to their symmetrical nature whiles odd harmonics remain in the system and need to be eliminated by the method of filtering or compensation techniques. Figure 2.1 (Ramon, 2015) illustrates typical voltage harmonic waveforms due to nonlinear loads.

Figure 2.1 Voltage Harmonic Waveforms as a Result of Nonlinear Loads

#### 2.2.2 Harmonic Current

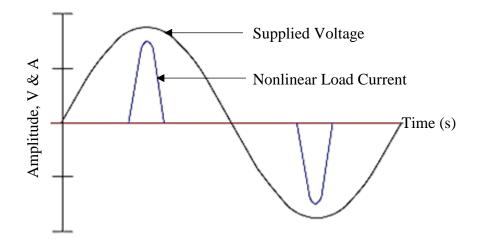

A load is considered nonlinear if the current drawn by the load will not be sinusoidal even when it is connected to a sinusoidal voltage. In this case such nonlinear current contains frequency components that are multiples of the power system frequency (Kamenka, 2014). Harmonics current are therefore caused by these nonlinear loads which lead to the disruption of the desired linear system. Figure 2.2 (Snehal and Dnyaneshwar, 2016) illustrates a typical non-sinusoidal nature of current waveform caused by nonlinear load.

Figure 2.2 Typical Current Waveform due to Nonlinear Load

#### 2.2.3 Harmonic Voltage

Voltage harmonics are caused by the current harmonics which distort the voltage waveform (Snehal and Dnyaneshwar, 2016). These harmonic currents interact with the impedance of the electrical power network to create voltage distortion that can affect the power network itself and the loads connected to it (Anon., 2014a). These voltage harmonics affect the entire system not just the loads which are causing them. The impact of voltage harmonics depends on the distance of the load causing the harmonics from the power source.

#### 2.2.4 Harmonic Distortion

In this modern world with changing technology, a few number of industries use rectifiers or converters, power supplies and other electronic devices to improve upon the quality of their products. These electronic devices introduce the distortion of the smooth sinusoidal wave of the supply current. This will actually make the flow of current not to be directly proportional to the supply voltage. These loads are often referred to as nonlinear loads. The non-linear loads usually lead to waveforms that are multiples of the fundamental frequency sine wave to be superimposed on the base (design) waveform. Hence, the frequency of the second harmonic is two times the fundamental and that of the third harmonics is three times the fundamental. Therefore, the combination of the sine wave with all the harmonic distortion.

#### 2.2.5 Harmonic Phase Sequences

Harmonics of different orders are said to have different phase sequences. In general terms, a phase sequence is the order of rotation of phase vectors relative to each other. Positive sequence harmonics have the same phase rotation as the fundamental component (i.e. 4<sup>th</sup>, 7<sup>th</sup>, 10<sup>th</sup>, .....). These harmonics circulate between the phases. Negative sequence harmonics have the opposite phase rotation with respect to the fundamental component (i.e. 2<sup>nd</sup>, 5<sup>th</sup>, 8<sup>th</sup>). These harmonics also circulate between the phases. Zero sequence harmonics do not produce a rotating field. These harmonics circulate between the phase and neutral or ground (i.e. 3<sup>rd</sup>, 6<sup>th</sup>, 9<sup>th</sup>,) unlike positive and negative sequence harmonics.

#### 2.2.6 Triplen Harmonics

Triplen harmonics are the odd integer multiples of the third harmonic waveform. Triplen harmonics are of particular concern because they are zero sequence harmonics. Electronic equipment generates more than one harmonic frequency. Some of these electronic equipment generate harmonics such as 3<sup>rd</sup>, 9<sup>th</sup>, 15<sup>th</sup> and 21<sup>st</sup> etc. Such harmonics are referred to as triplen harmonics. Triplen harmonics can do more harm than distortion of voltage waveforms; hence it has been recognised as a major concern to both engineers and building designers. This is because triplen harmonics can lead to overheating of wiring in buildings, nuisance tripping, overheating of transformer units, and random end-user equipment failure.

#### 2.2.7 Harmonic Indices

Harmonic indices are the index values developed for assessing the quality of current and voltage waveforms due to the presence of harmonics. The two most commonly used indices for measuring the harmonic content of a waveform are the total harmonic distortion and total demand distortion. Harmonic component in power systems can be calculated for, by considering it as a percentage of the fundamental or a percentage of the root mean square (rms) value of the total current as shown in Equation (2.1) (Kamenka, 2014).

$$I_{h} = \frac{I_{n}}{I_{1}} \times 100 \%$$

(2.1)

where,  $I_n$  = amplitude of the current harmonic in amperes

$I_1$  = amplitude of the fundamental current (or rms value of the total current) in amperes

Equation (2.1) can be applied to harmonic voltage as well.

#### Total harmonic distortion

Total Harmonic Distortion (THD) is the term used to describe the level of harmonic content in the power distribution system. It is therefore defined as the ratio of the sum of the powers of all harmonic components to the power of the fundamental frequency. The THD value is normally used for low, medium, and high voltage systems.

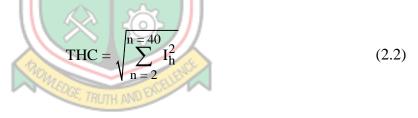

#### Total harmonic current

Total Harmonic Current (THC) is the accumulated currents of the orders 2 to 40 that contribute to the distortion of the current waveform. This value is particularly useful in determining the required characteristics for installation of modern active harmonic filters (Kamenka, 2014). The expression for THC is given in Equation (2.2) (Kamenka, 2014).

#### Total harmonic distortion of current

Total Harmonic Distortion of current (THD<sub>I</sub>) usually specifies the total harmonic current distortion of the waveform. This value is defined as the percentage ratio of the harmonic current to the fundamental (non-harmonic) current measured at a load point at the particular moment when the measurement is taken. For example, the sum of all the current harmonics being calculated in relation to the fundamental frequency current up to the 40<sup>th</sup> harmonic order can be calculated as shown in Equation (2.3) (Kamenka, 2014).

$$\text{THD}_{I} = \frac{\sqrt{\sum_{n=2}^{n=40} I_{h}^{2}}}{I_{1}} \times 100\% = \frac{\sqrt{I_{h2}^{2} + I_{h3}^{2} + \dots + I_{hn}^{2}}}{I_{h1}} \times 100\% = \frac{\text{THC}}{I_{1}} \quad (2.3)$$

#### Total harmonic distortion of voltage

The Total Harmonic Distortion of voltage (THD<sub>V</sub>) also specifies the total magnitude of the voltage distortion. This value is also defined as the percentage ratio of the harmonic voltage to the fundamental (non-harmonic) voltage. Equation (2.4) (Kamenka, 2014) expresses the sum of all the voltage harmonics being calculated in relation to the fundamental frequency voltage up to the  $40^{\text{th}}$  harmonic order.

$$THD_{V} = \frac{\sqrt{\sum_{n=2}^{n=40} V_{h}^{2}}}{V_{1}} \times 100\% = \frac{\sqrt{V_{h2}^{2} + V_{h3}^{2} + \dots + V_{hn}^{2}}}{V_{h1}} \times 100\%$$

(2.4)

#### Total demand distortion

Total Demand Distortion (TDD) is the ratio of the measured harmonic current to the full load fundamental current. The full load fundamental current is the total amount of nonharmonic current consumed by all the loads on the system when the system is at peak demand. So the TDD is the THD of current being normalised to the maximum demand load current. TDD is equal to THDi only if the system is at full load condition. The expression of the TDD is as presented in Equation (2.5) (Kamenka, 2014).

$$TDD = \frac{\sqrt{\sum_{n=2}^{n=40} I_h^2}}{I_L} \times 100\% = \frac{\sqrt{I_{h2}^2 + I_{h3}^2 + \dots + I_{hn}^2}}{I_L} \times 100\%$$

(2.5)

#### 2.3 Harmonics Filtering Techniques

Filters are mainly employed in power systems in order to reduce excessive harmonics in the system. The major technique of employing harmonic filters is to utilise power electronic switches to produce equal and opposite current signals that eliminate the harmonic currents from the nonlinear loads (Ekhlas *et al.*, 2015). The resulting effect of harmonics being injected into the power system due to the rapid increase in consumers' nonlinear load calls for a greater concern. The technique is to install filters that can suppress or interact with the power system harmonic (Mikkili and Panda, 2016). In general, harmonic filters can be classified as passive or active filters. Passive filtering technique is most commonly used in industries because it provides a low impedance path to harmonic currents over a certain

frequency bandwidth and also cheaper in cost. The more sophisticated active filtering concepts operate in a wider frequency range (De La Rosa, 2015). Active filters are designed to inject harmonic currents to counterbalance existing harmonic components as they show up in the distribution system. Active filters comprise of DC, AC, series, and parallel configurations. Hybrid filters are a combination of passive and active filtering schemes. The harmonic components in the system usually are of a very large magnitude of current. Compensation of harmonics can therefore be achieved by the use of filters (Contractor *et al.*, 2015).

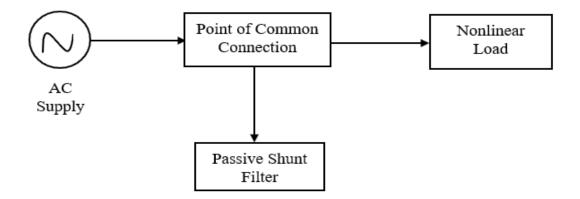

#### 2.3.1 Passive Filtering of Harmonics

Passive filters are filter circuits that are tuned to a specific frequency, which means that this filter circuit offers a high impedance path to the fundamental frequency and a low impedance path to ground for the higher specific frequencies (Sahana, 2015). Passive filters cannot be used in power systems where the harmonic component keeps changing or varies randomly (Mikkili and Panda, 2016). Passive filters are generally classified into three main categories as passive series, passive shunt and passive hybrid filters. The choice of any of these configurations depends on the level of harmonic content in the system and most importantly, the advantages of each of them. The use of passive filters has the advantage of reducing undesirable harmonics in the system and also provide reactive power compensation in order to improve the system performance. The disadvantage of using these filters is that, it allows the occurrence of resonance with line impedance. Also, it requires a lot of calculations since tuning frequency is less accurate and also, they are heavy and bulky. Figure 2.3 (Sahana, 2015) shows a schematic diagram of the connection of passive filters.

Figure 2.3 Schematic Diagram of the Connection of Passive Filter

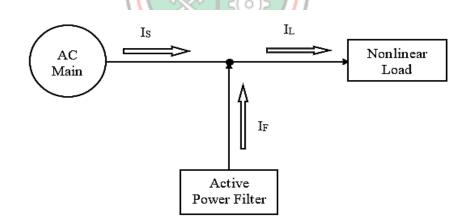

#### 2.3.2 Active Filtering of Harmonics

Active filters are filter circuits which in their operation monitor continuously the harmonic current being generated by the nonlinear loads and hence generate exactly the same waveform corresponding to the load. In short, active filters inject equal and opposite harmonics into the power system to cancel those generated by the nonlinear loads (De La Rosa, 2015; Mikkili and Panda, 2016). The basic principle of active filters is based on the utilisation of power electronic technologies for generating the required harmonic level which can cancel that produced by the nonlinear load. The merits of active filters are as follows: Ability to cancel out harmonics, block resonance, management of reactive power, accurate and easy tuning, small size and more importantly, they can be used when harmonic component keeps changing or varies randomly. Unlike passive filters, active filters are very expensive and also, there is a possibility of developing inherent harmonics due to the power electronic devices. Active filters are classified into three main categories namely; shunt active, series active and hybrid active filters. Shunt active filters can further be classified based on the type of converter, topology and the number of phases. The converter used can either be current source converter or voltage source converter (Bhim et al., 2015). Figure 2.4 (Sahana, 2015) shows a schematic diagram of active shunt filter with nonlinear load.

Figure 2.4 Schematic Diagram of Active Shunt Filter with Nonlinear Load

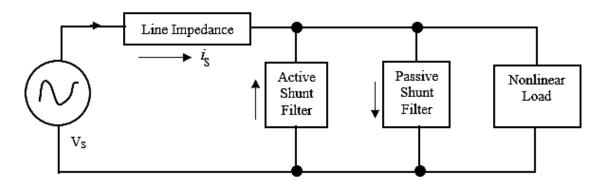

#### 2.3.3 Hybrid Harmonic Filter

Hybrid harmonic filter is a type of filter circuit which is designed by combining both passive and active filter circuits together for filtering harmonic components in power systems. Hybrid harmonic filters are used in power systems where passive filters can be used for constant or static loads whereby that of active filters can be used for mitigating harmonics produced by randomly changing loads. The combined circuit is generally referred to as Hybrid Active Power Filter (HAPF) (Rooh *et al.*, 2015). Figure 2.5 (Bhim *et al.*, 2015) shows a schematic diagram of hybrid power filter as a combination of active shunt and passive shunt filters. Hybrid power filters have a very large number of configurations each of which depends on the non-linear load present in the system. Among a lot, only four of these configurations are mostly used due to a number of benefits and also, in order to meet the requirements of various types of nonlinear loads. These four configurations are: A combination of passive series and passive shunt filters, a combination of series connected passive shunt and active shunt filters, a combination of active series and passive shunt filters.

Figure 2.5 Schematic Diagram of Hybrid Power Filter as a Combination of Active Shunt and Passive Shunt Filters

## 2.4 Two-Level Voltage Source Converter for Harmonic Mitigation

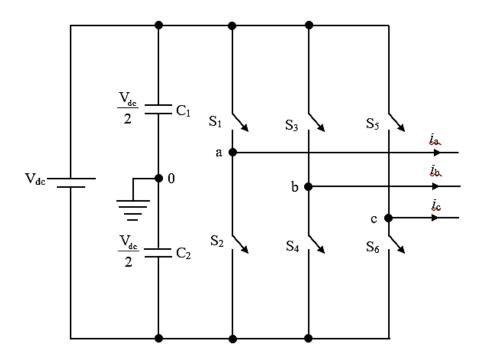

Voltage Source Converter (VSC) is the type of circuit that permits the conversion from dc voltage source to ac voltage output and it is often referred to as inverter (Euzeli and Edison, 2015). In this circuit design, a dc capacitor is normally provided at the dc source side which stabilises the dc voltage. The 2-level converter is capable of generating two output voltage levels by switching between,  $+V_{dc}$  and  $-V_{dc}$  (Anaya-Lara *et al.*, 2014). Even though the circuit design of the converter is simple with small sizes of dc capacitor, its basic output ac waveform contains high harmonic content and also has higher switching frequency due to the dc capacitor size which leads to higher switching losses. For medium and high-voltage applications, Pulse Width Modulation (PWM)-based two-level converters are limited due to current and voltage ratings of the switching devices (Das, 2015).

In order to overcome the effect of harmonics, multilevel converters were introduced. Multilevel converters (inverters) are capable of offering better performance than the conventional two-level converters (Andrzej, 2016). The multilevel converter has the advantages of low pulse height, reduced harmonic content and lower switching frequency with much lower switching power losses (Yuriy *et al.*, 2016). The use of multilevel converter improves the quality of the ac output voltage generated. This is because with multilevel converters, the quality of the output voltage increases as the number of voltage levels increases. Figure 2.6 (Karthikeyan *et al.*, 2014; Euzeli and Edison, 2015) shows the schematic diagram of a three phase two-level voltage source converter.

Figure 2.6 Three Phase Two-Level Voltage Source Converter

## 2.5 Multilevel Converter for Harmonic Mitigation

Multilevel inverter is a power electronic device which is capable of providing the desired alternating voltage level at the output where DC voltage is taken as the input. A dc to ac power conversion is performed by inverter circuits. These inverter circuits are usually supplied from a DC source whiles its output is an AC voltage which has a fundamental component with adjustable frequency and magnitude. Inverters can be classified according to the type of source and these are: Voltage Source Inverter (VSI) and Current Source Inverter (CSI). Active power filters for harmonic current mitigation in a power system

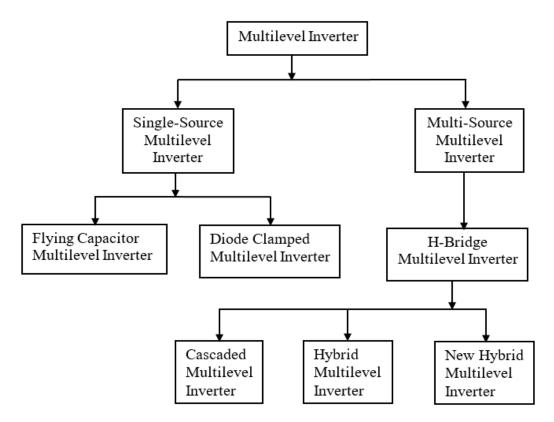

represent an example of dc-to-ac power conversion. Multilevel converters (i.e. dc to ac inverters) offer better performance than two-level inverters (Andrzej, 2016). The performance of a multilevel inverter in terms of ratings, efficiency and operation mainly depends on its topology and the type of control algorithm used in its PWM controller (Gaddafi *et al.*, 2016). The most commonly used multilevel inverter topologies are: Diode clamped and flying capacitor topologies for single source multilevel inverters, and then the H-Bridge for the multi-source case. The H-bridge multilevel inverter can be cascaded, hybrid or new hybrid. The mitigation of harmonics is usually achieved through the switching design (i.e. switching angles are calculated in a special way) of the multilevel inverters when considering the various topologies. Figure 2.7 (Murugesan *et al.*, 2016) shows the types of multilevel inverter topologies.

**Figure 2.7 Types of Multilevel Inverter Topologies**

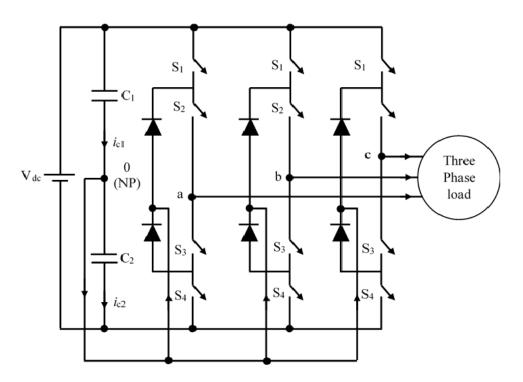

## 2.5.1 Diode Clamped Multilevel Inverter

The diode clamped type of multilevel inverter uses capacitors in series to divide the DC bus voltage into a set of voltage levels. To produce n-levels of the phase voltage, an n-level diode clamped multilevel inverter needs n-1 capacitors on the DC bus. For a DC bus voltage

of  $V_{dc}$ , the voltage across each capacitor will be  $V_{dc}/3$  (Gaddafi *et al.*, 2016). The main advantage of this type of multilevel inverter is that in terms of three phase system, the entire phases share a common dc bus, which minimises the capacitance requirements of the converter. The main disadvantage is that real power flow is difficult for a single inverter because the intermediate dc levels will tend to overcharge or discharge without precise monitoring and control. The number of clamping diodes required is by calculation related to the number of levels, which can also be cumbersome for units with a higher number of levels. Figure 2.8 (Euzeli and Edison, 2015) shows the schematic diagram of three level diode (or neutral) clamped inverter with voltage source.

Figure 2.8 Schematic Diagram of Three Level Diode Clamped Inverter

## 2.5.2 Flying Capacitor Multilevel Inverter

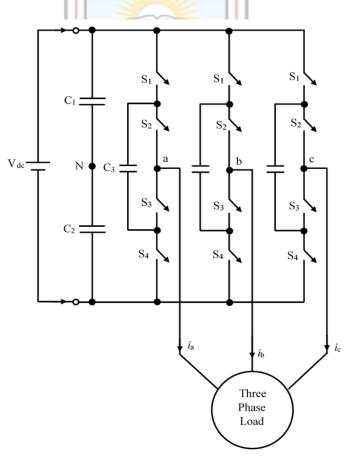

The capacitor clamped type of the multilevel inverter is also called flying capacitor due to the fact that the capacitors in the circuit usually float with respect to the potential of the earth (Akhila *et al.*, 2016). The flying capacitor multilevel inverter requires a large number of capacitors in order to clamp the device (switch) voltage to one capacitor voltage level. On condition that all the capacitors are of equal value, an n-level inverter according to Murugesan *et al.* (2016) will require a total number of (n-1)(n-2)/2 clamping capacitors per

phase leg in addition to (n-1) main dc bus capacitors. If the voltage of the main dc–link capacitor is  $V_{dc}$ , the voltage of innermost capacitor, the innermost two devices is  $V_{dc}$ / (n-1). The voltage of the innermost capacitor will be  $V_{dc}$ / (n-1) +  $V_{dc}$ / (n-1) =  $2V_{dc}$ / (n-1) and so on. Each next clamping capacitor will have the voltage increment of  $V_{dc}$ / (n-1) from its immediate inner single voltage level.

The advantage of this type of multilevel inverter is that phase redundancies are available for balancing the voltage levels of the capacitors, real and reactive power flows are controlled. The large number of capacitors enables the inverter to ride through short duration outages. The main disadvantages of this type of topology is that, it is very complicated to track the voltage levels for all of the capacitors. Also, the large number of capacitors needed are more expensive and bulky than clamping diodes in multilevel diode-clamped converters. Packaging is also difficult in inverters with a high number of levels (Murugesan *et al.*, 2016). Figure 2.9 (Andrzej, 2016) shows the schematic diagram of three level flying (clamped) capacitor inverter.

Figure 2.9 Schematic Diagram of Three Level Flying Capacitor Inverter

#### 2.5.3 Cascaded H-Bridge Multilevel Inverter

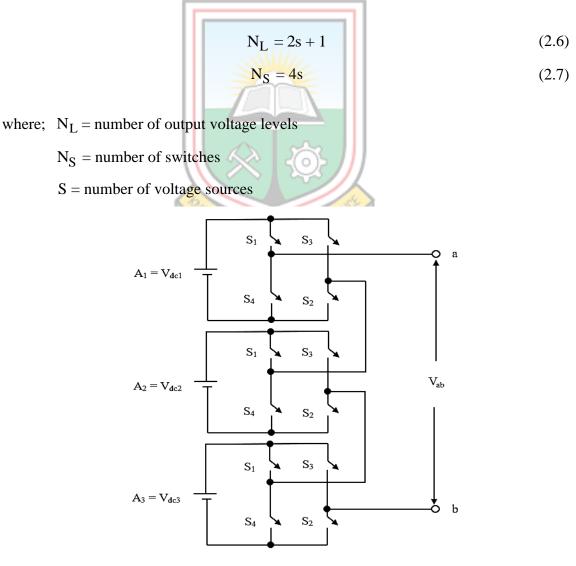

The cascaded H-bridge multilevel inverter is based on addition of separate dc power supply voltages. In this type of multilevel inverter topology, each of the separate voltage sources (i.e.  $V_{dc1}$ ,  $V_{dc2}$ ,  $V_{dc3}$  .....) are connected in cascade with other sources through a special H-bridge circuit associated with it. The main advantage of this cascaded multilevel inverter is the series H-bridge for modularised layout and packaging (Boudaghi and Tousi, 2012). Also, it is cheaper in terms of cost. Its main disadvantage is that, it needs a separate dc source for each of the H-bridges. The use of solar battery or fuel cell where rectifiers and input transformers are employed is an example of such converters (Yuriy *et al.*, 2016). Figure 2.10 (Murugesan *et al.*, 2016) illustrates the schematic diagram of cascaded H-bridge multilevel inverter. The number of output voltage levels and number of switches can be calculated using Equation (2.6) and Equation (2.7) (Murugesan *et al.*, 2016), respectively.

Figure 2.10 Schematic Diagram of Cascaded H-Bridge Multilevel Inverter

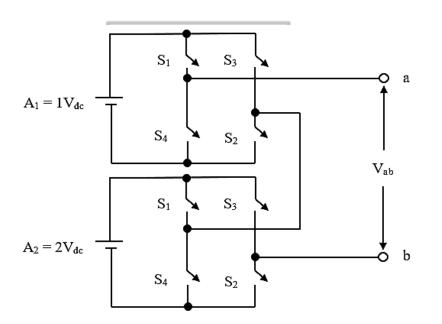

#### 2.5.4 Hybrid H-Bridge Multilevel Inverter

The hybrid H-bridge multilevel inverter is similar to that of cascaded H-bridge multilevel inverter. The only difference between the two topologies is that it has a high number of levels with lesser number of bridges if compared to the cascaded H-bridge multilevel inverter. The main advantages of hybrid multilevel inverter is that, it has a high number of levels with reduced number of bridges and the dc sources are not of equal value. Figure 2.11 (Murugesan *et al.*, 2016) illustrates the schematic diagram of hybrid H-bridge multilevel inverter. Its number of output voltage levels and number of switches can be calculated using Equation (2.8) (Murugesan *et al.*, 2016).

$$N_{\rm L} = 2^{\rm S+1} - 1 \tag{2.8}$$

Figure 2.11 Schematic Diagram of Hybrid H-Bridge Multilevel Inverter

## 2.6 Custom Power Devices for Mitigation of Harmonics

A Custom Power Device (CPD) is the type of Flexible AC Transmission System (FACTS) controller that is mainly used in power distribution systems (Ambarnath *et al.*, 2012), hence the name CPD. They are power electronic devices or static controllers used in power distribution systems that are rated from 1 kV to 38 kV with the aim of supplying certain levels of reliable power or the quality of power that is needed by electric power consumers

whose equipment are very sensitive to power variations (Devaraju *et al.*, 2010). The custom power devices are: Distribution Static Compensator (DSTATCOM) for compensating load reactive power and current harmonics; Dynamic Voltage Restorer (DVR) for compensating problems associated with voltage and Unified Power Quality Conditioner (UPQC) for both current and voltage compensation (Mani and Naidu, 2015).

## 2.6.1 Distribution Static Compensator

DSTATCOM is one of the custom power devices which is commonly used for mitigating current-based power quality problems, especially in power distribution systems (Bhim *et al.*, 2015). Shunt active power filter in current control mode is referred to as DSTATCOM. These shunt active power filters are used to mitigate harmonic currents in nonlinear loads. DSTATCOMs are basically classified into three types, namely, single-phase two wire, three-phase three wire, and three phase four wire configurations in order to meet the requirement of the various types of loads. DSTATCOM in general is used in power distribution systems to either generate or absorb reactive power depending on the problem concerned. DSTATCOM for mitigating harmonics in power distribution systems can also be classified based on the type of converter used.

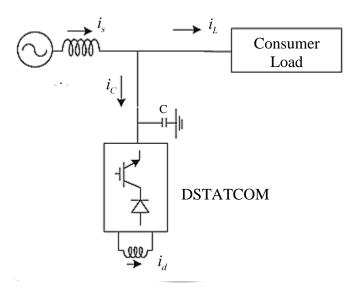

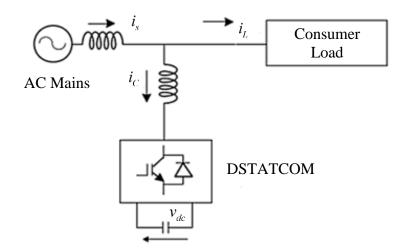

The DSTATCOM is made up of coupling transformer with a leakage reactance, a three phase Insulated Gate Bipolar Transistor (IGBT) VSI and a DC capacitor. The DSTATCOM employs an inverter in order to convert the DC link voltage  $V_{dc}$  on the capacitor to a voltage source of adjustable magnitude and phase. Therefore, the D-STATCOM can be treated as a voltage controlled source. The DSTATCOM can also be seen as a current controlled source (Kishore and Reddy, 2014). The main function of the VSI is to produce a sinusoidal AC voltage with minimal harmonic distortion from a DC voltage. The principle of operation of the DSTATCOM is as follows: The voltage is compared with the AC bus voltage system ( $V_s$ ). When the magnitude of AC bus voltage is above that of the VSI ( $V_c$ ); the AC system sees the DSTATCOM as inductance connected to its terminals. Otherwise, if the VSI voltage magnitude is above that of the AC system sees the DSTATCOM as capacitance to its terminals. If the voltage magnitudes are equal, the reactive power exchange is zero. If the DSTATCOM has a DC source or energy storage device on its DC side, it can supply real power to the power system. This can be achieved by adjusting the phase angle of the DSTATCOM terminals and the phase angle of the AC power system. When phase angle of the AC power system leads the VSI phase angle, the DSTATCOM absorbs the real power from the AC system. If the phase angle of the AC power system lags the VSI phase angle, the DSTATCOM supplies real power to AC system. Figures 2.12 and 2.13 (Bhim *et al.*, 2015) illustrate current source converter based DSTATCOM and voltage source converter based DSTATCOM, respectively. A diode is used in series with the IGBT self–commutating device for the reverse voltage blocking. The voltage source converter has self-supporting DC voltage bus with a large DC capacitor. It has the advantage of being expanded to a multiple level to enhance the performance with lower switching frequencies.

Figure 2.12 Current Source Converter-based DSTATCOM

Figure 2.13 Voltage Source Converter-based DSTATCOM

#### 2.6.2 Dynamic Voltage Restorer

Dynamic Voltage Restorer (DVR) is a custom power device mainly used in solving voltage related problems in power distribution systems and it is normally connected in series to the load (Mahmoud *et al.*, 2013). The function of this device is to protect sensitive loads from experiencing voltage sag or swell, which is an interruption in the system. DVR is a fast, flexible and efficient solution for mitigating voltage sag and voltage swell problems (Vivek and Monika, 2016). DVR is a recent and very essential custom power device for compensation of voltage generated power quality problems in power distribution systems. Its main function is to quickly boost up the load-side voltage in the event of a voltage sag in order to avoid any power disruption to that load. Figure 2.14 (Shazly *et al.*, 2013) illustrates the location of DVR in a power distribution network.

Figure 2.14 Location of a Dynamic Voltage Restorer

## 2.6.3 Unified Power Quality Controller

The Unified Power Quality Controller (UPQC) is a very versatile custom power device that can inject current in shunt circuit and voltage in series circuit simultaneously in a dual control mode. Therefore, it can perform the functions of both voltage and current based compensation, respectively (Pawar *et al.*, 2016). Due to its versatility (compensating the unbalanced conditions of both voltage and current), fast response, nominal cost and high reliability amongst the custom power devices, it is generally considered as the best option for solving power quality problems in power distribution systems (Desale *et al.*, 2014).

#### 2.7 Proportional-Integral-Derivative Control

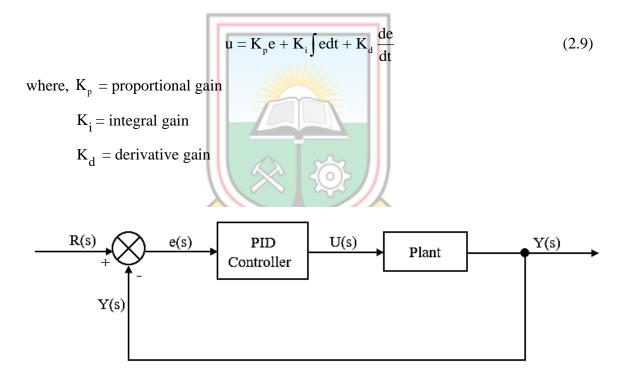

The design of a control system is about creating a dynamic system that can behave in a predetermined way in order to give a desired output. The controller modifies the behaviour of the system so that it can behave in a specific desirable way over a period of time. The aim of feedback control is to make sure that, the output of the plant, Y(s) follows the reference input R(s) as close as possible. The basic working principle of the Proportional-Integral-Derivative (PID) controller in a closed-loop system using the block diagram is shown in Figure 2.15. The variable e(s) represents the tracking error, that is, the difference between the desired input value R(s) and the actual output Y(s). This error signal serves as the input to the PID controller, and the controller computes its output signal U(s) based on the PID algorithm. For the PID controller, U(s) is expressed using Equation (2.9).

Figure 2.15 Block Diagram of Unity Feedback Control System

Proportional gain,  $K_p$  has the effect of reducing the rise time but will not eliminate the steady-state error. Integral gain,  $K_i$  has the effect of eliminating the steady-state error, but it may make the transient response worse. Derivative gain,  $K_d$  increases the stability of the system, reducing the overshoot, and improving the transient response. The effects of each gain parameter  $K_p$ ,  $K_i$  and  $K_d$  on a closed-loop system are summarised into Table 2.1.

| SN | Gain<br>Parameter | Rise Time    | Overshoot | Settling Time | Steady State<br>Error |

|----|-------------------|--------------|-----------|---------------|-----------------------|

| 1. | Kp                | Decrease     | Increase  | Small Change  | Decrease              |

| 2. | K <sub>i</sub>    | Decrease     | Increase  | Increase      | Eliminate             |

| 3. | K <sub>d</sub>    | Small Change | Decrease  | Decrease      | Small Change          |

Table 2.1 Effect of PID Controller Gain Parameters on a Control System

(Source: Tehrani and Mpanda, 2015)

## 2.8 Review of Related Works on the Mitigation of Harmonics in Power Distribution Systems

Geetha and Devi (2012) in their work focused on the control techniques employed for DSTATCOM. They considered VSC-based DSTATCOM employed in power distribution systems. They did comparison between phase shift control and AC/DC link voltage schemes which were incorporated to control the STATCOM. In conclusion, it was proposed that DSTATCOM's control scheme should be done such that, a complete reactive power compensation, power factor correction and voltage regulation of the harmonics can also be checked, in order to achieve improved power quality levels at the distribution end.

Malleswararao *et al.* (2015) investigated a five level cascaded H-bridge multilevel inverterbased DSTATCOM with fuzzy logic controller in 11 kV power distribution system for compensation of reactive power and harmonic mitigation. Cascaded H-bridge inverter was considered due to its advantages of reduced harmonic distortion and reduction in number of switches thereby reducing switching losses. In their investigation, d-q reference frame theory was used to generate reference compensating currents for the DSTATCOM whiles fuzzy logic controller was used for capacitor dc voltage regulation. In addition, Level Shifted Pulse Width Modulation (LSPWM) and Phase Shifted Pulse Width Modulation (PSPWM) techniques were implemented to analyse the performance of the cascaded Hbridge inverter. The source voltage, load voltage, source current, load current, power factor simulation results under nonlinear loads were investigated for LSPWM. From the tabulated results, it was concluded that fuzzy-based DSTATCOM controller is better than the PI controller techniques.

Mahesh *et al.* (2016) in their investigation considered multilevel inverter as DSTATCOM for harmonic compensation. A shunt active power filter as cascaded H-bridge multilevel

inverter DSTATCOM with phase shifted PWM technique was proposed to mitigate harmonic components in the source currents. The mathematical modelling of the system and the controller design were done using Synchronous Reference Frame (SRF) theory. Their results showed that, the cascaded H-bridge multilevel inverter and DSTATCOM have the advantage of mitigating harmonics in the source current of power distribution system to meet IEEE 519–1992 standards.

Srikanth (2013) presented a modified SRF method for real time generation of compensating current for harmonic mitigation, active and reactive power compensation. He proposed a fast-acting DC-link voltage controller based on the energy of the dc-link capacitor. A comparison between conventional and fast acting DC-link voltage controller for improving the transient performance of the compensator for nonlinear and unbalanced loads to improve power quality was then carried out. By the use of fast-acting DC-link voltage controller, harmonic filtering, voltage regulation, load balancing and unity power factor were all achieved.

Kalyani and Kamaraju (2015) proposed a scheme for new multilevel state-space modelbased DSTATCOM together with a deadbeat prediction controller and five-level cascaded multilevel inverter to solve the problem of harmonic mitigation of nonlinear loads in distribution systems. PI controller was used to regulate the dc capacitor voltage at a reference value. The use of cascaded multilevel H-bridge inverter for DSTATCOM helped to decrease the output harmonics by increasing the number of output voltage levels of the device.